Arbitrary Waveform Generator (AWG)

Capabilities and Applications

December 8, 2022

Innovation for the Next Generation

Confidential and Proprietary: Shared under NDA

#### Target applications

- High-speed SerDes, transceivers, and amplifier validation

- Receiver jitter and noise tolerance testing

- General time domain measurements of high-speed digital communication signals

- Support for compliance PHY and protocol stress testing of MIPI C/D-PHY, MIPI M-PHY, PCIe5, USB4 and others

- Coherent 400ZR module development and validation

- BER and FER tester

#### Key features and instrument capabilities

- 4-channel Differential AWG (0.1-64 GB) and User Defined Modulation

- Programmable RJ and SJ (dual tones) Jitter injection in AWG mode

- Cross talk emulation by BUJ jitter injection

- ISI emulation (LPF) and de-emphasis in AWG mode

- 2 Dual-Channel (I/Q) Differential PPG (25-64 GB) with NRZ/PAM4 modulation

- Coherent signals generation for QAM modulation

- Built-in 7-tap or 60-tap FFE in PPG mode

# **Electrical Specifications**

| Parameter                              | Specifications                                                     |

|----------------------------------------|--------------------------------------------------------------------|

| TX Coupling                            | AC coupled                                                         |

| Channel Impedance (Diff)               | 100 Ohm                                                            |

| TX/RX connectors                       | SMPM (M)                                                           |

| TX 3dB Bandwidth                       | 35 GHz                                                             |

| Reference clock Output                 | Baud Rate/48 or Baud Rate/24 (<1.2GHz max)                         |

| Clock out amplitude (SE/Diff)          | 0.6/1.2 Vpp                                                        |

| Clock input amplitude (SE/Diff)        | 0.5/1 Vpp                                                          |

| Clock Input Validated Range            | 150 - 160 MHz                                                      |

| Instrument Automatic Shutoff           | 85 °C                                                              |

| Recovery from over-temperature shutoff | Manual reboot of the system and instrument temperature below 85 °C |

| Setup time / Reboot                    | 38 s                                                               |

| Normal Operating Temperature           | 0 - 65 °C                                                          |

| Power                                  | 12 V, 1.5 A                                                        |

# Arbitrary Waveform Generator specifications

| Parameter                        | Specifications                                                                                                                                                                                                                                         |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

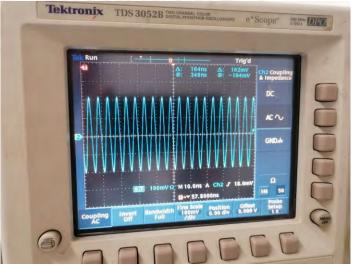

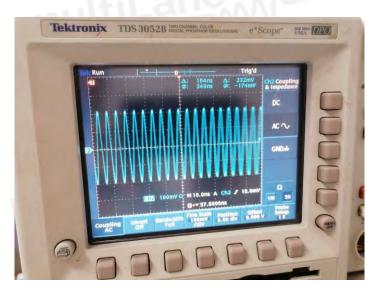

| Tx Maximum Amplitude (Sine wave) | 1050 mVppd                                                                                                                                                                                                                                             |

| Bit Rates                        | 1 – 64 Gbps                                                                                                                                                                                                                                            |

| Vertical Resolution              | 8 bits                                                                                                                                                                                                                                                 |

| Modulation                       | User-defined                                                                                                                                                                                                                                           |

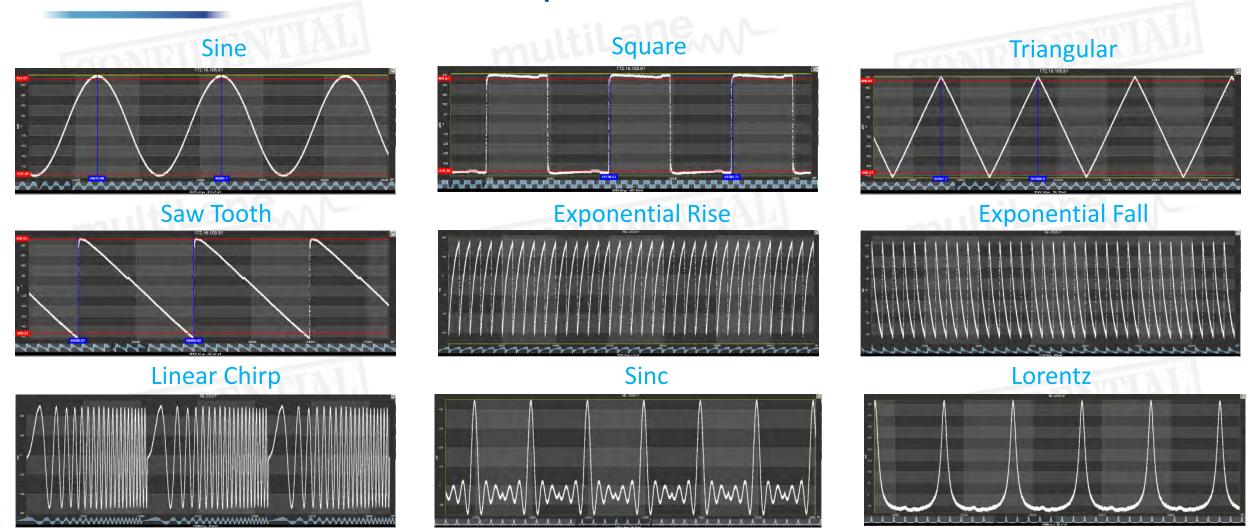

| Pre-programmed Waveforms         | PRBS 7, PRBS 9, Square wave, triangular Wave, sinewave, multi-tone, linear chirp, log chirp, sawtooth, exponential rise, exponential decay, Sinc, Lorentz, Surge, Damped Oscillation, Stairs, Serial Data, half-sine, Distorted sinewave and Gaussian. |

| Memory Depth                     | 33.6 kSa per channel                                                                                                                                                                                                                                   |

# Pulse Pattern Generator specifications

| Parameter                   | Specifications                            |

|-----------------------------|-------------------------------------------|

| Bit Rates                   | 25 – 64 GBd                               |

| Modulation                  | NRZ and PAM4                              |

| Tx Maximum Amplitude at 26G | 750 mVppd (350 mVppd in calibration mode) |

| Tx Maximum Amplitude at 53G | 500 mVppd (300 mVppd in calibration mode) |

| Patterns                    | PRBS 7/9/11/15/20/23/29/31/35/39/41/47    |

| TX Amplitude Adjustment     | Steps of 1 mV                             |

| TX Equalization             | FFE 3 taps or 7 taps                      |

| Pre-Emphasis Resolution     | ±168 steps                                |

| Equalizing Filter Spacing   | 1UI                                       |

# 4080 Product – AWG Examples

Innovation for the next generation

# 4080 Product – AWG Examples

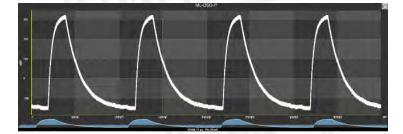

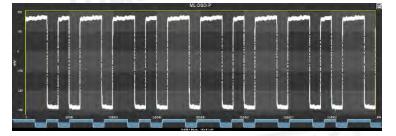

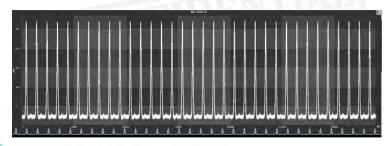

#### Surge

**Serial Data**

Gaussian

**Damped Oscillation**

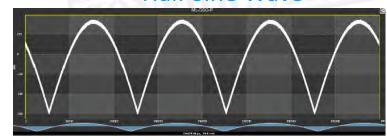

Half Sine Wave

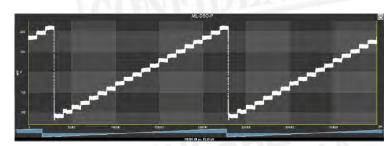

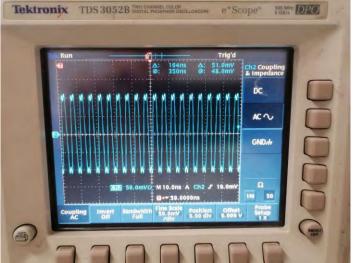

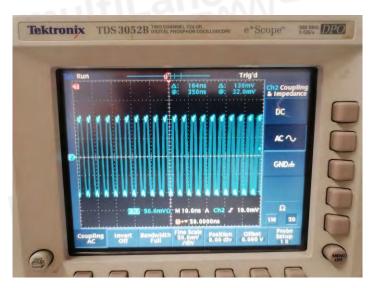

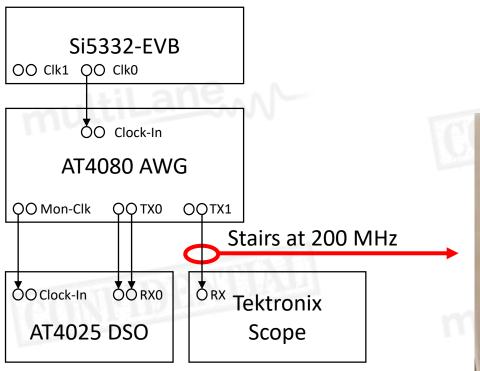

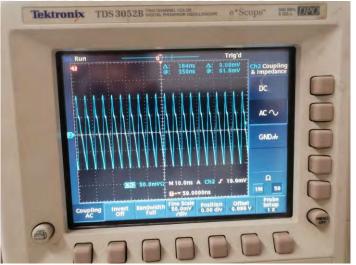

**Stairs**

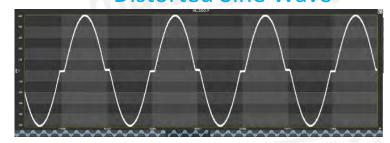

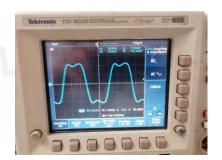

**Distorted Sine Wave**

# **Applications Examples**

- USB 4.0 (NRZ, 20 Gbps)

- USB 4.1 (PAM3, 25.6 GBd)

- PCle gen5 (NRZ, 32.5 Gbps)

- PCle gen6 (PAM4, 32.5 GBd)

- ThunderBolt

- Ethernet 112G/Lane

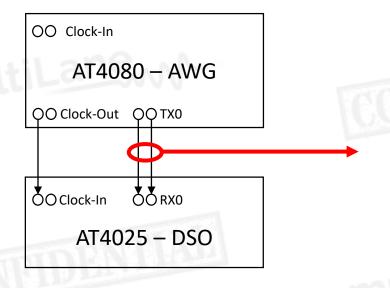

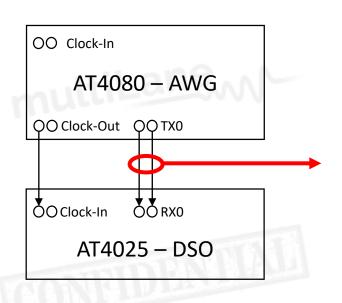

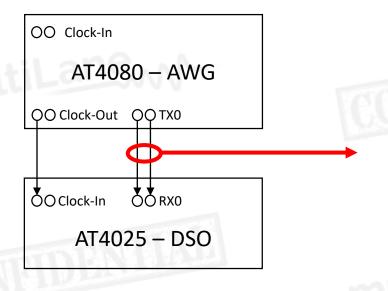

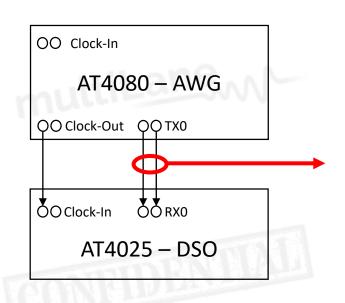

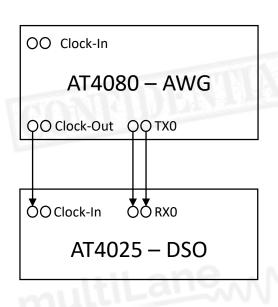

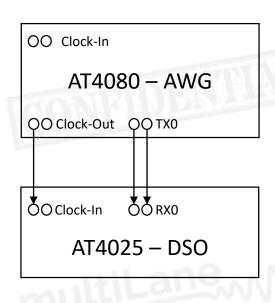

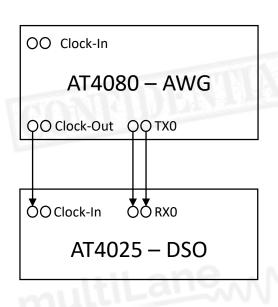

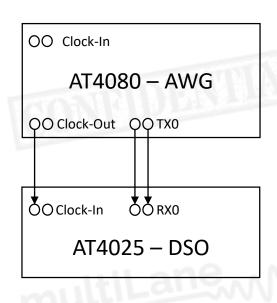

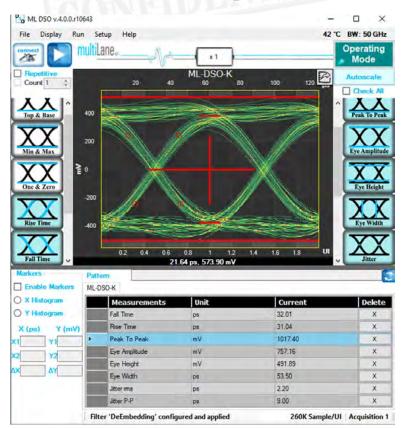

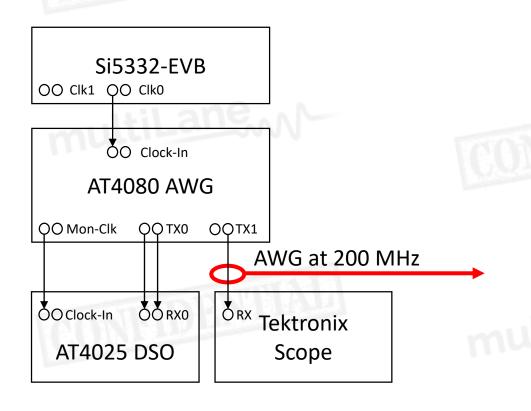

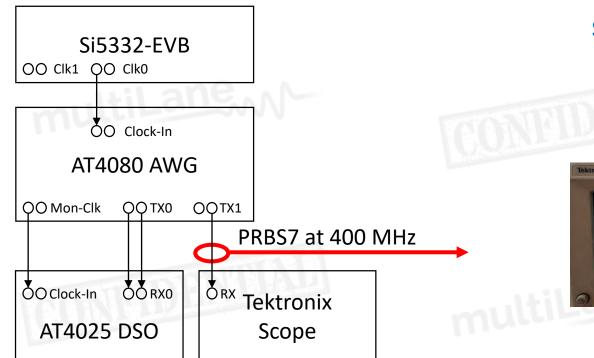

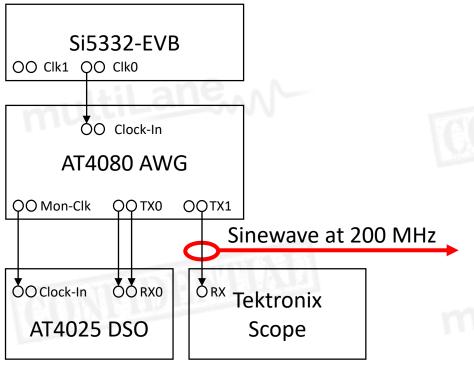

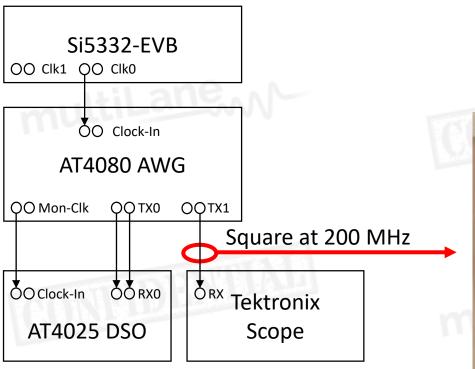

#### Setup

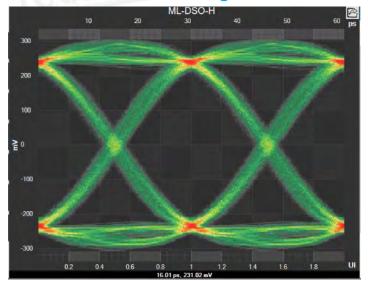

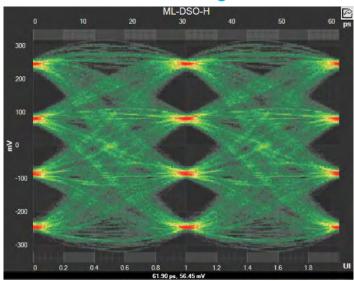

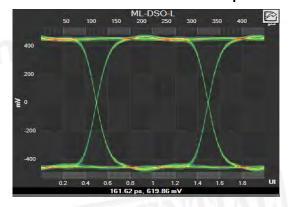

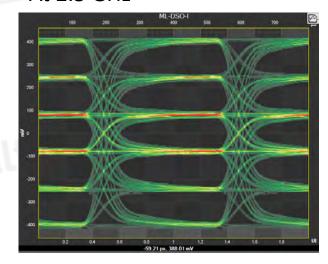

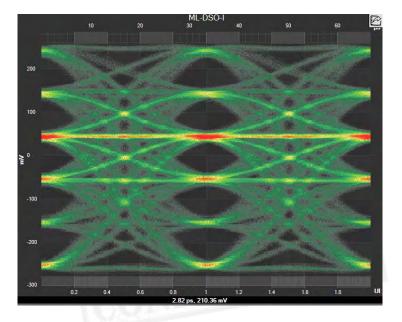

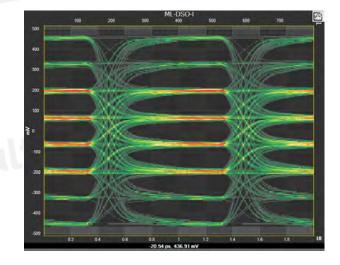

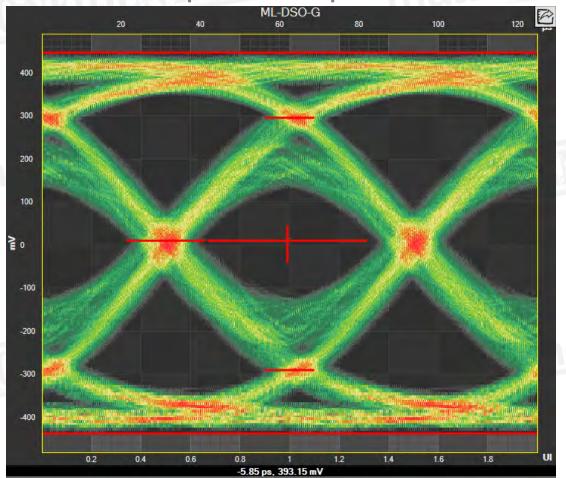

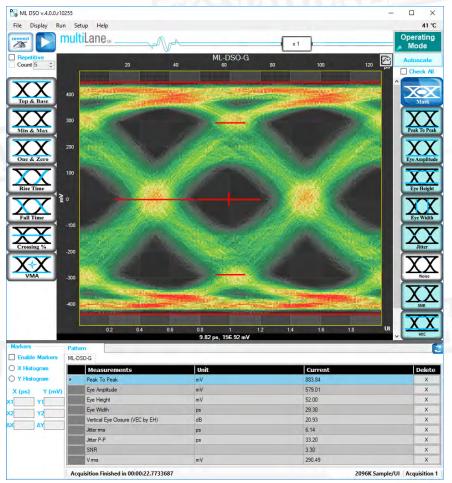

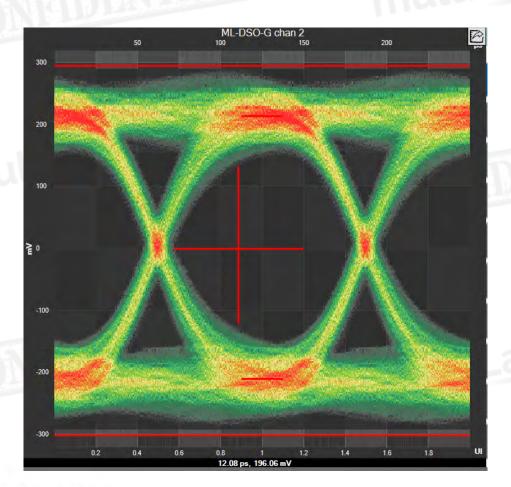

32.5G NRZ Signal

Confidential and Proprietary: Shared under NDA

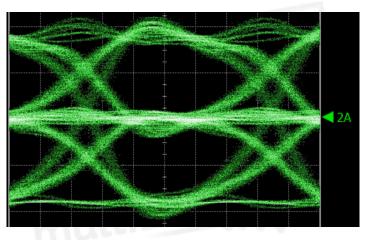

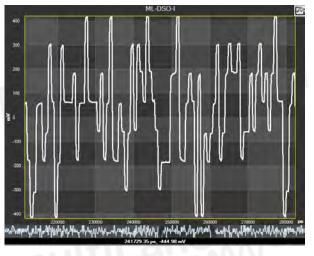

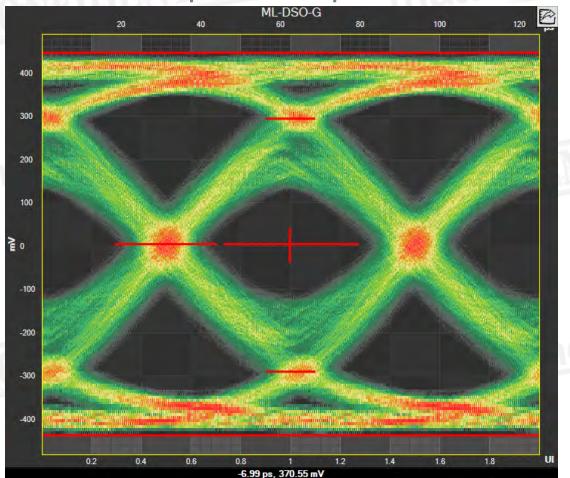

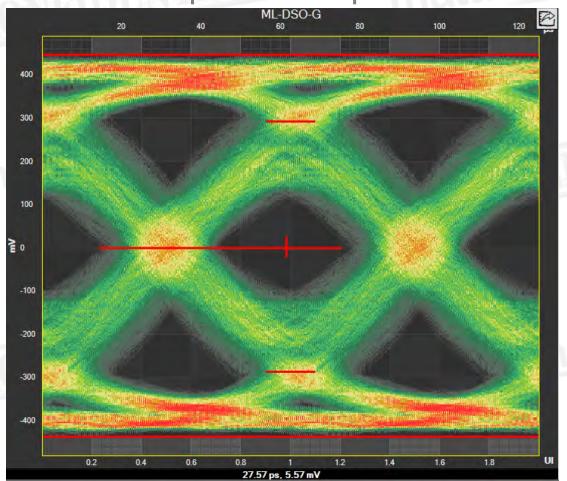

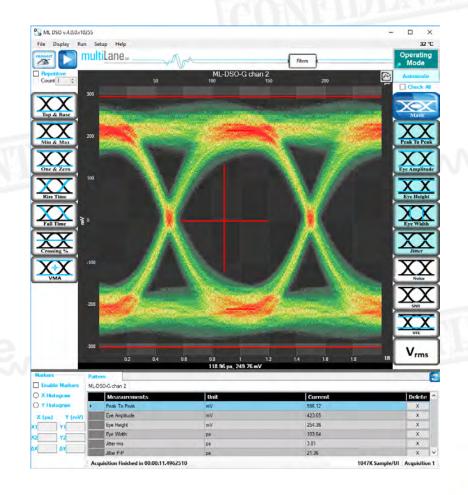

26 GBd PAM3 Signal

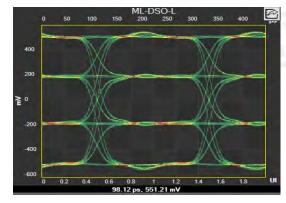

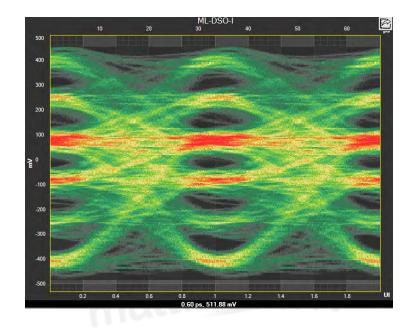

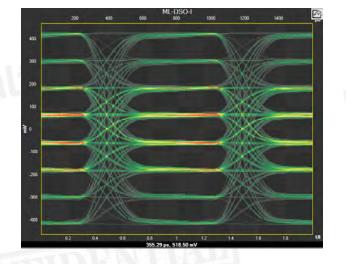

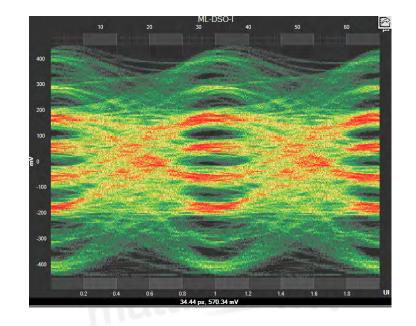

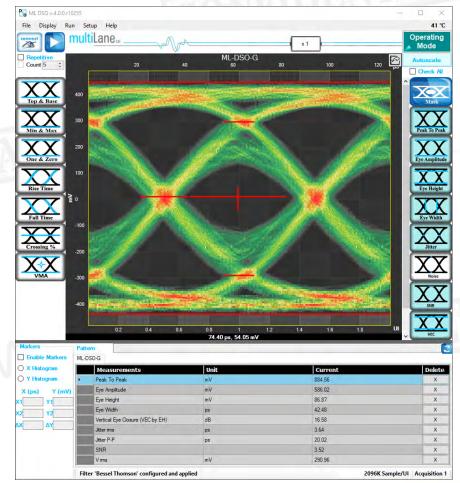

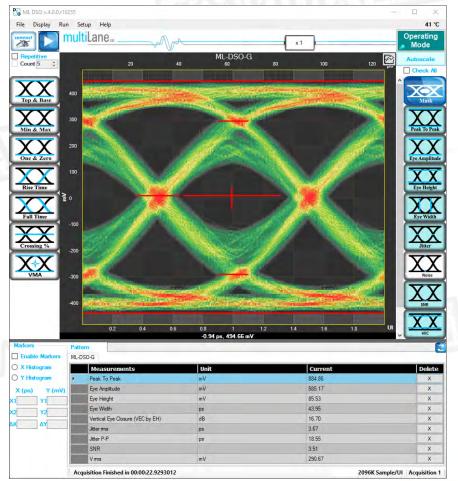

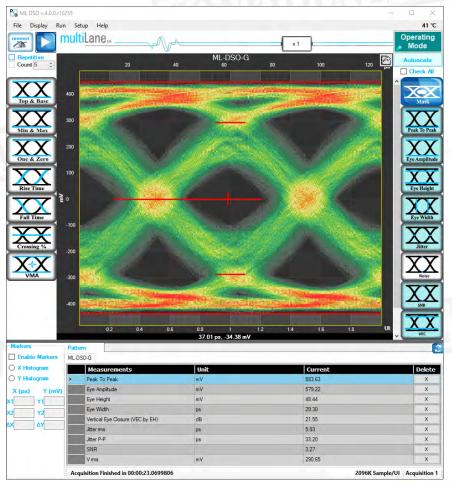

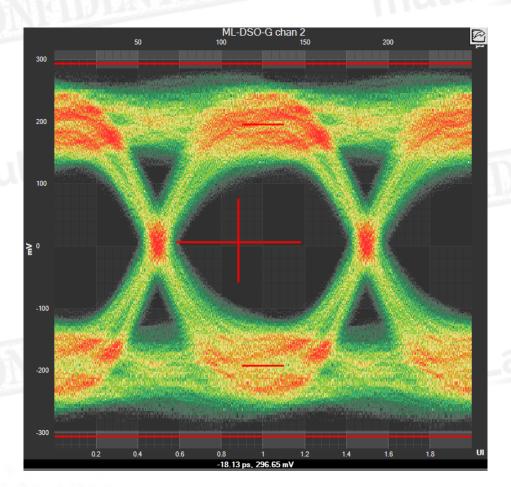

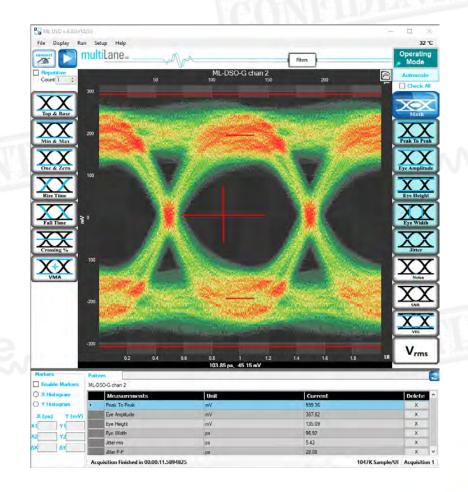

32.5G PAM4 Signal

#### PAM4 Editor

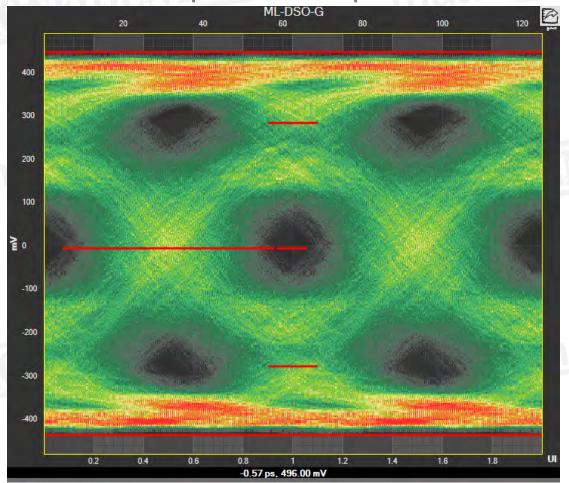

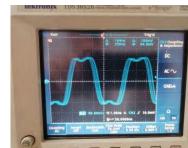

## Reshaping PAM4 Signal

Ability to reshape PAM4 signal using AWG, with the following:

- Level mismatch ratio (RLM)

- Duty cycle distortion

- Amplitude

- Rise time

- Fall time

# **Simulation** PAM-4 Editor NRZ PRBS9 26.5625G (BW=26 GHz)

Confidential and Proprietary: Shared under NDA

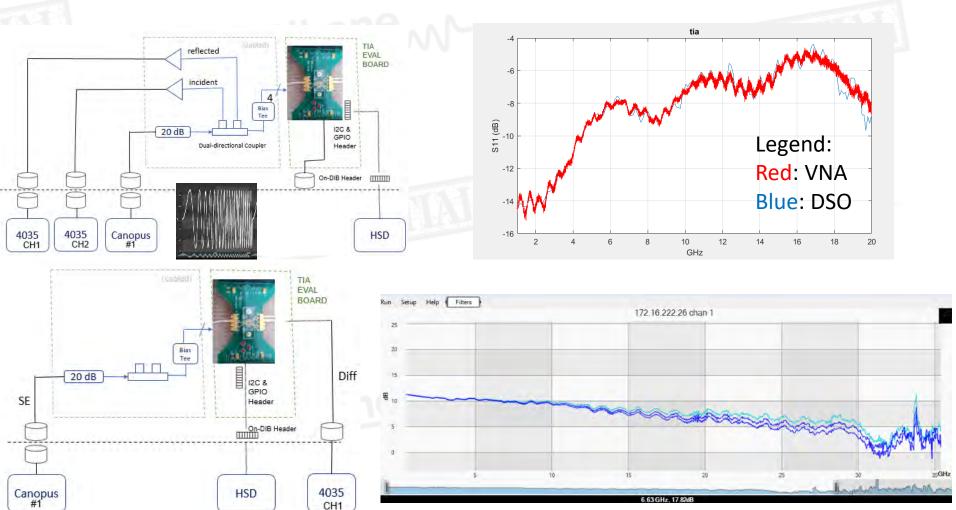

# S11 and S21 using 4080

S11: Canopus source with Chirp function and directional couplers

S21: amplifier bandwidth vs peaking

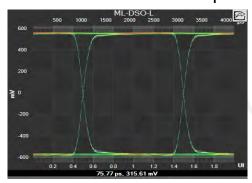

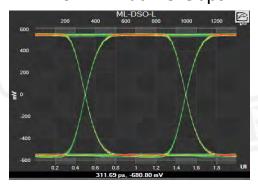

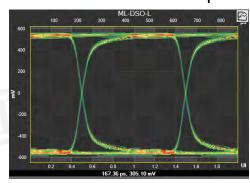

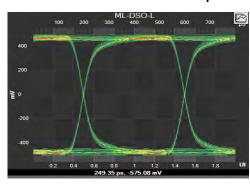

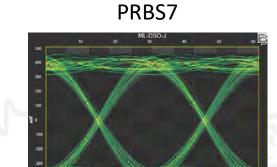

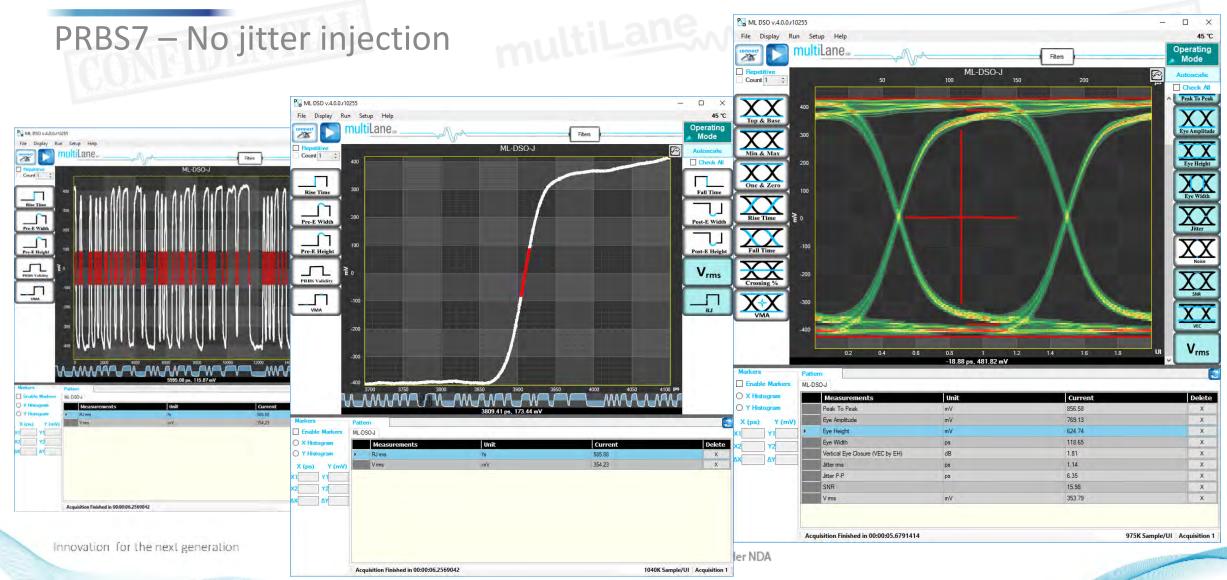

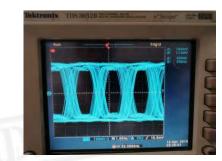

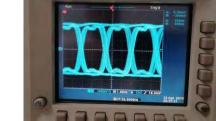

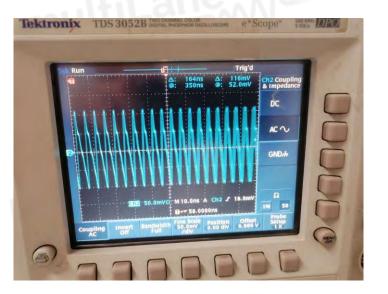

#### Compliance Test Patterns – PRBS7 patterns generated in AWG mode

PRBS7 NRZ at 480 Mbps

PRBS7 NRZ at 1.5 Gbps

PRBS7 NRZ at 2.3 Gbps

PRBS7 NRZ at 2.5 Gbps

PRBS7 NRZ at 6 Gbps

PRBS7 NRZ at 6.5 Gbps

PRBS7 NRZ at 10 Gbps

PRBS7 NRZ at 16 Gbps

## MIPI C-PHY Compliance Test Patterns

PRBS7 NRZ at 4.5 Gbps

PRBS7 PAM4 at 4.5GS/s

MIPI C-PHY 3-level signaling at 4.5 GS/s

MIPI C-PHY 3-level signaling at 6.5 GS/s

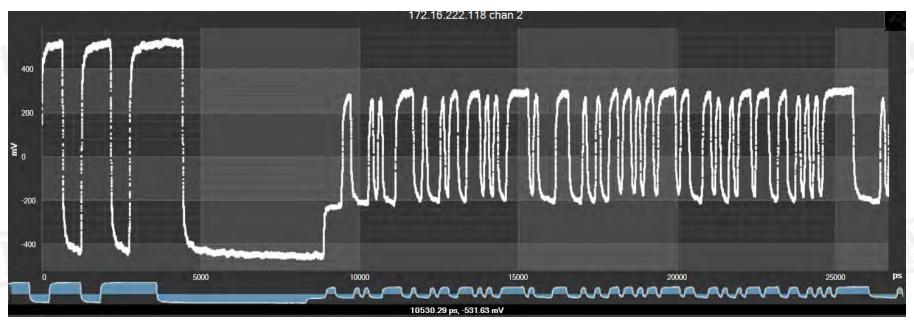

# MIPI C-PHY/D-PHY Compliance Testing

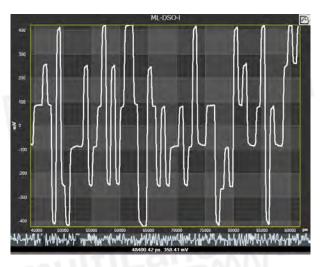

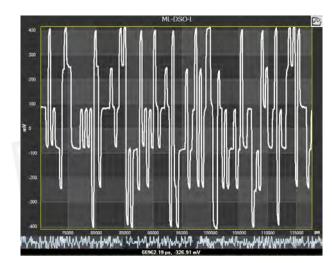

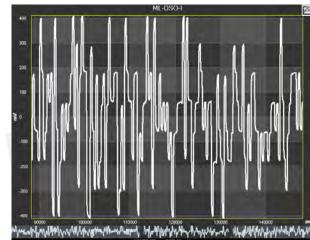

Generation of LP (Low Power) and HS (High Speed) signals in AWG mode

Example of HS PRBS7 at 7.14375 GS/s with LP square wave

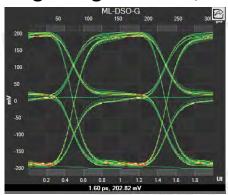

NRZ

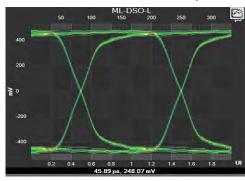

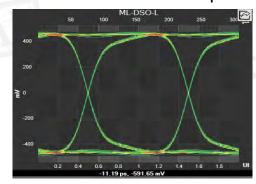

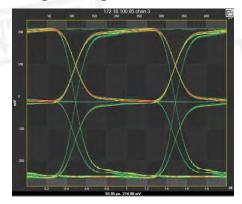

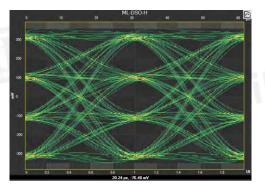

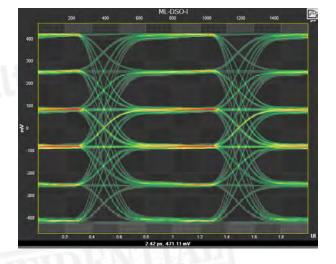

# PCIe Gen5 and Gen6 PRBS Patterns – NRZ and PAM4 at 32 GS/s

PAM4

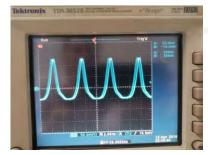

#### PAM6 Generation in PPG mode

#### At 1.25 GHz

At 2.5 GHz

## PAM6 Generation in PPG mode At 30 GHz

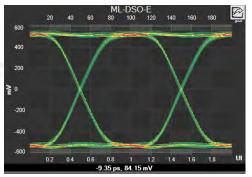

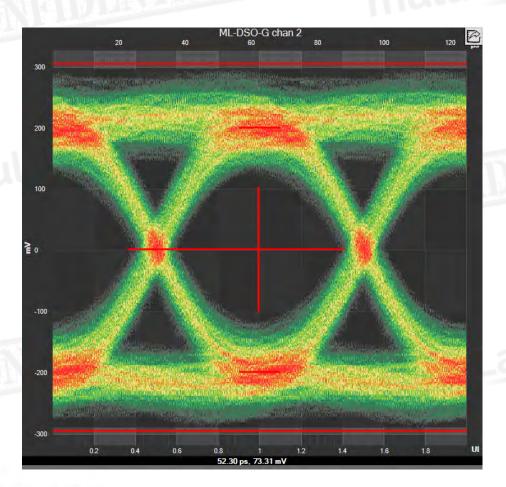

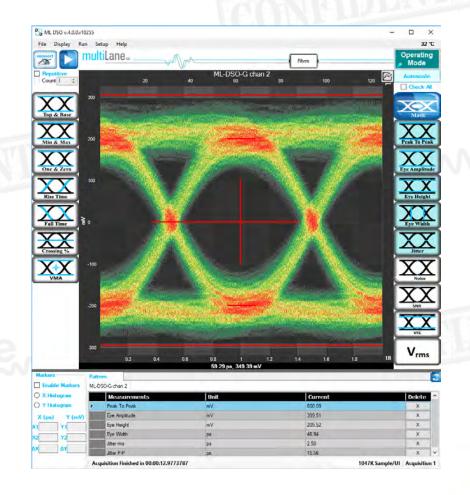

#### Without Pre-Equalization

With Pre-Equalization

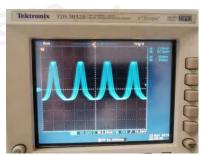

#### PAM8 Generation in PPG mode

#### At 1.25 GHz

At 2.5 GHz

#### PAM8 Generation in PPG mode

At 30 GHz

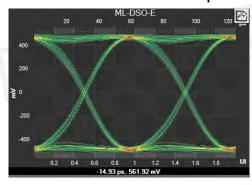

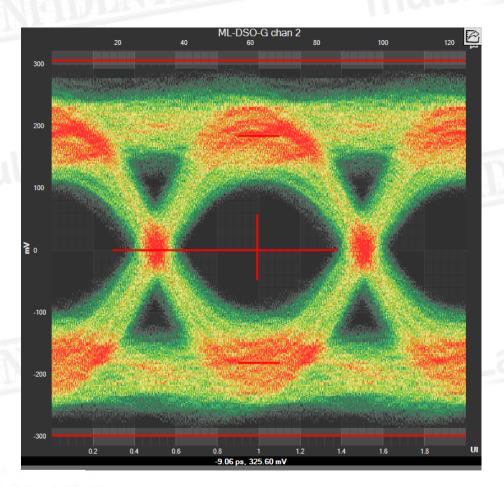

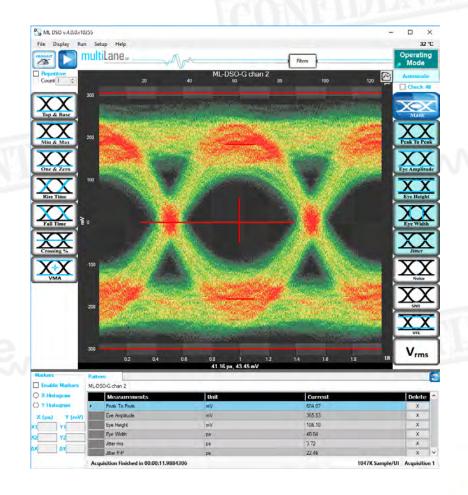

#### Without Pre-Equalization

With Pre-Equalization

Custom FFE applied FIR 90 taps - 3 taps per UI

# 4080 Product – Product Capabilities and Applications

Compliance Test Patterns Generation for PCIe Gen 3 and 4

4080 Product Capabilities for PHY compliance and stressed Eye testing

- Random Jitter (RJ) injection by software

- Sinusoidal Jitter (SJ) injection by software (both single and dual tones options)

- Inter-Symbol Interference (ISI) emulation by software

- Cross-talk emulation by Bounded Uncorrelated Jitter (BUJ) injection by software

- De-embedding s-parameters by applying customized patterns after pre-processing

- Spread-Spectrum Clocking supported for PCIe compliance testing

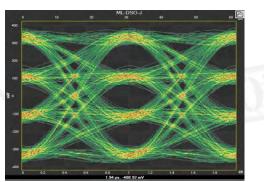

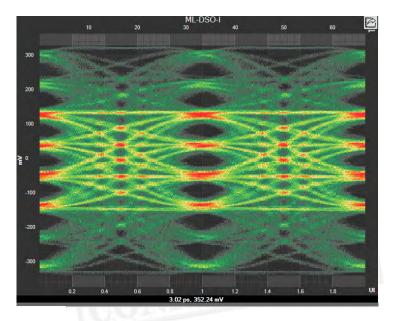

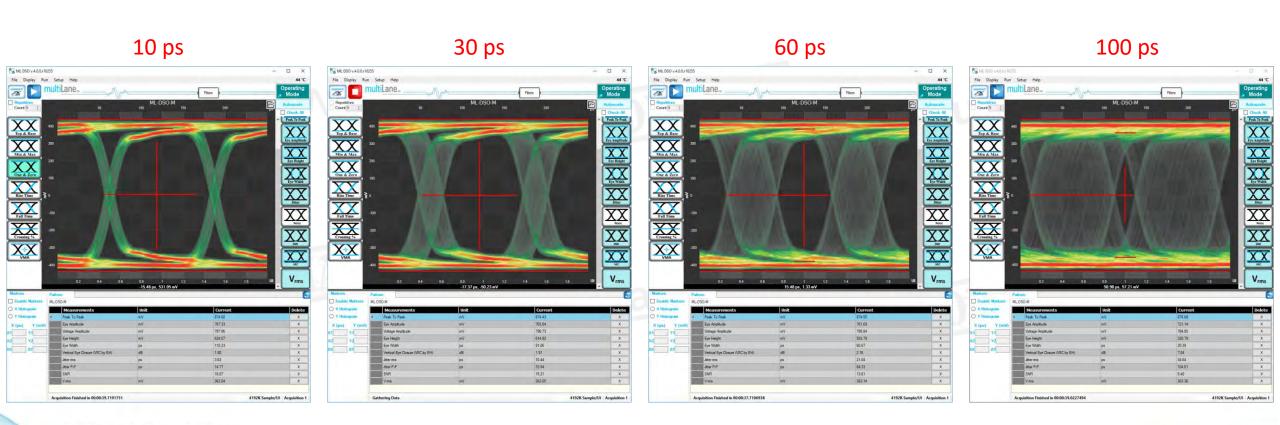

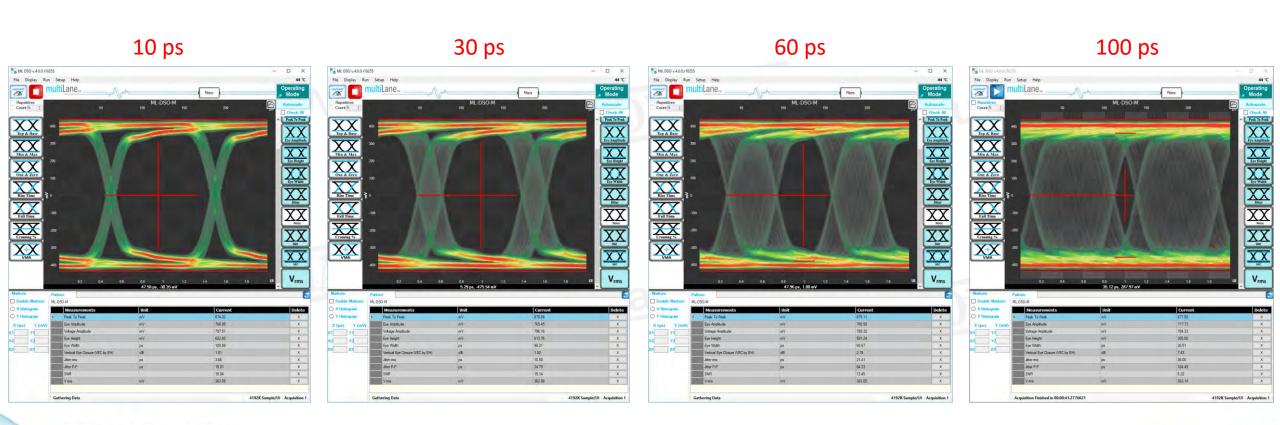

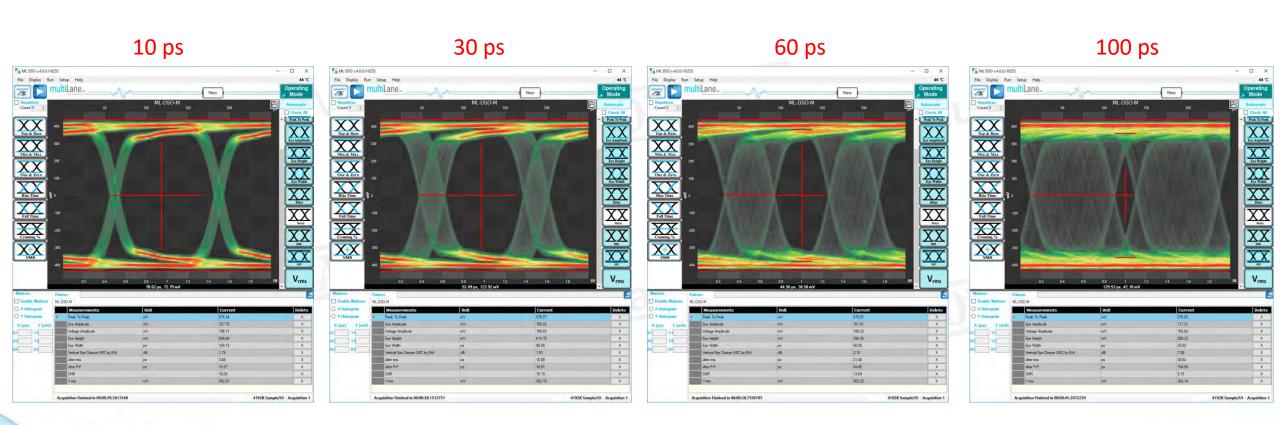

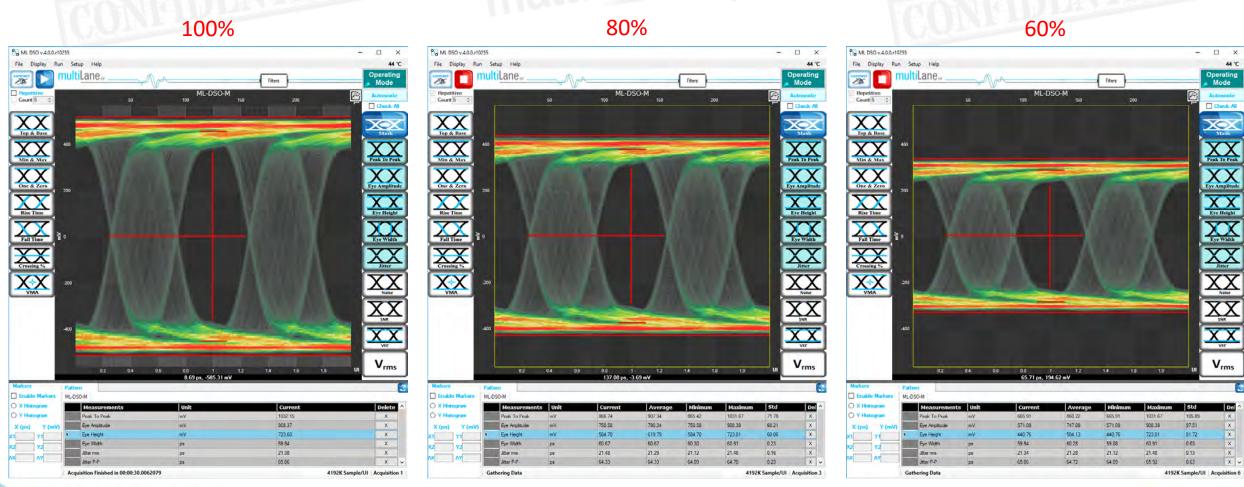

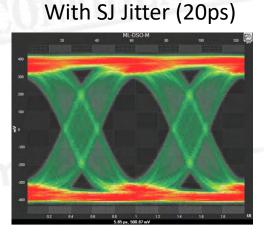

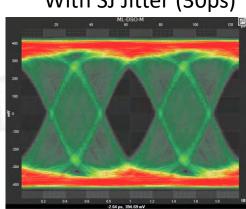

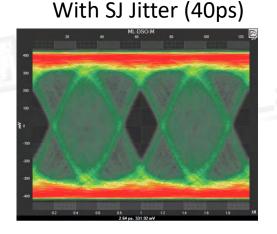

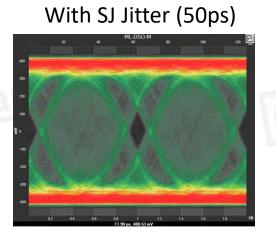

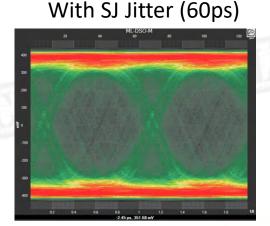

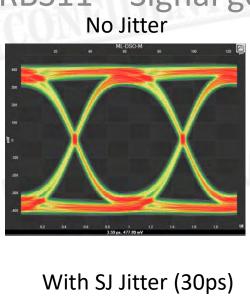

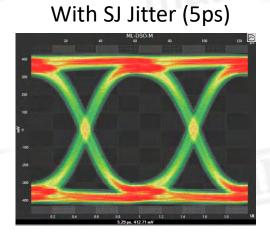

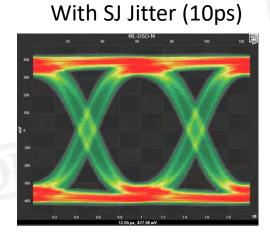

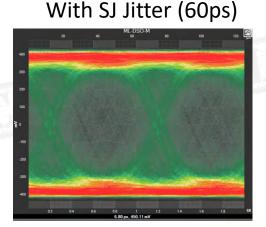

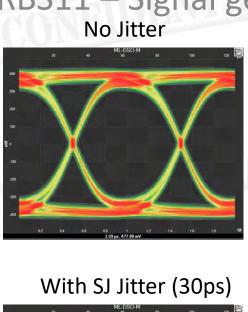

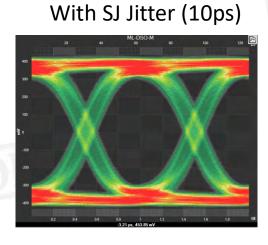

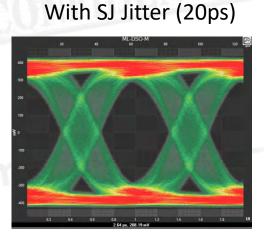

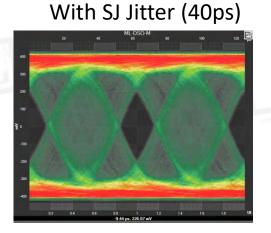

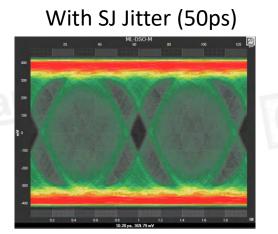

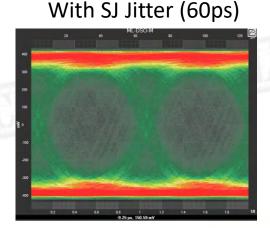

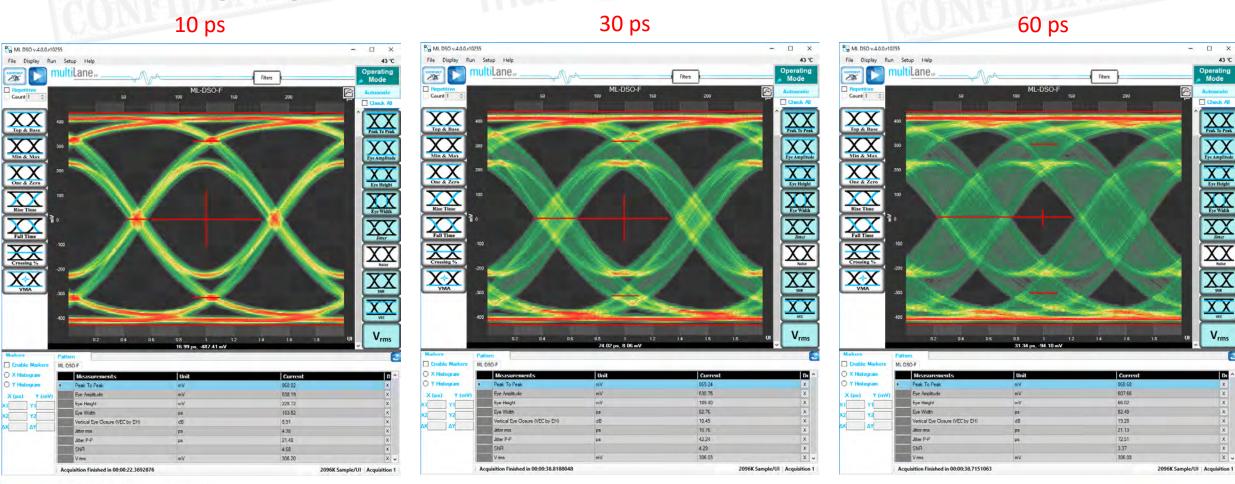

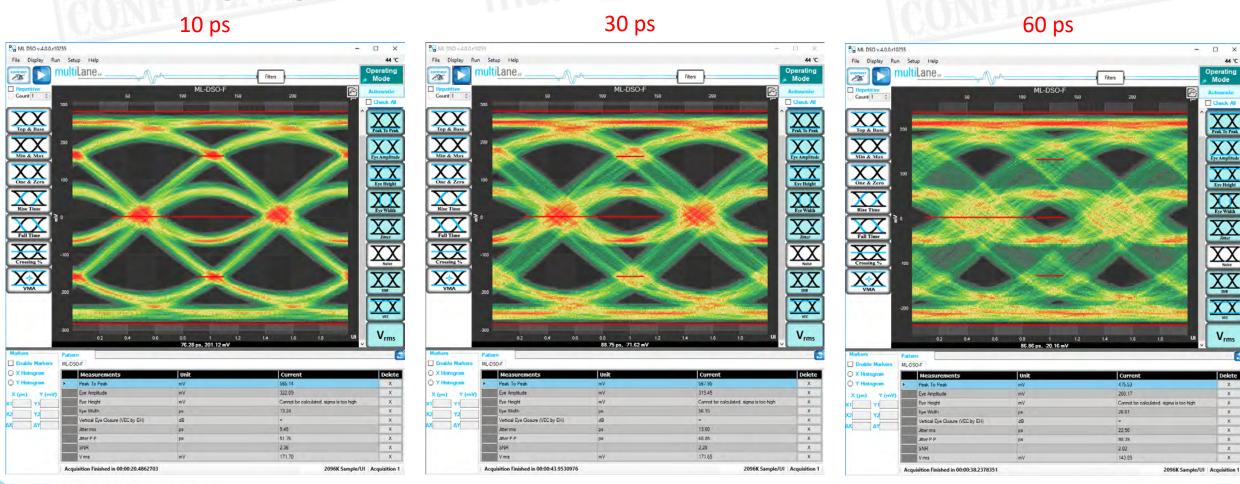

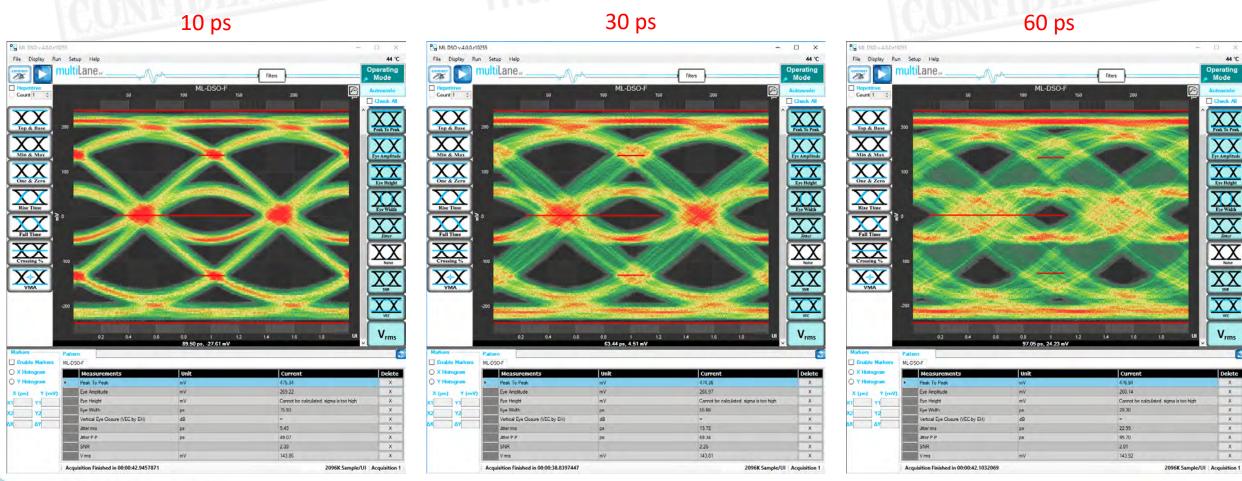

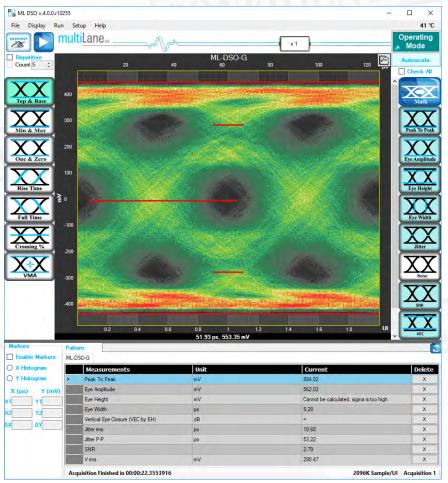

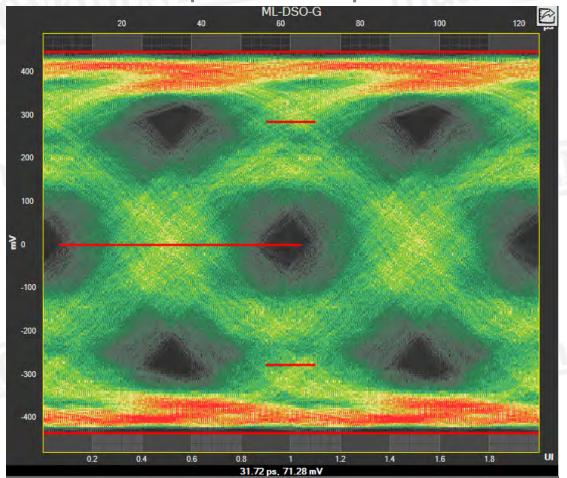

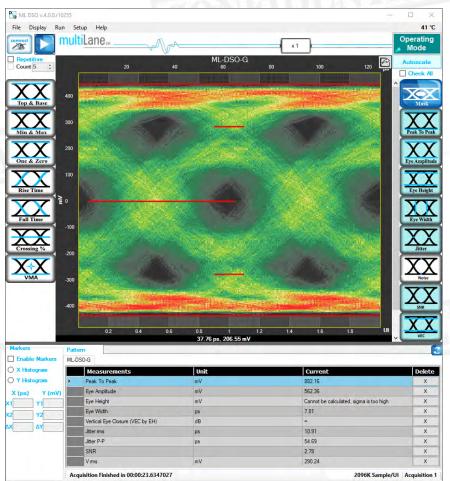

#### Jitter Measurements – PRBS 11

Single tone Jitter injection by software for PCIe Gen 3 and Gen 4

Jitter injected by software (60 ps)

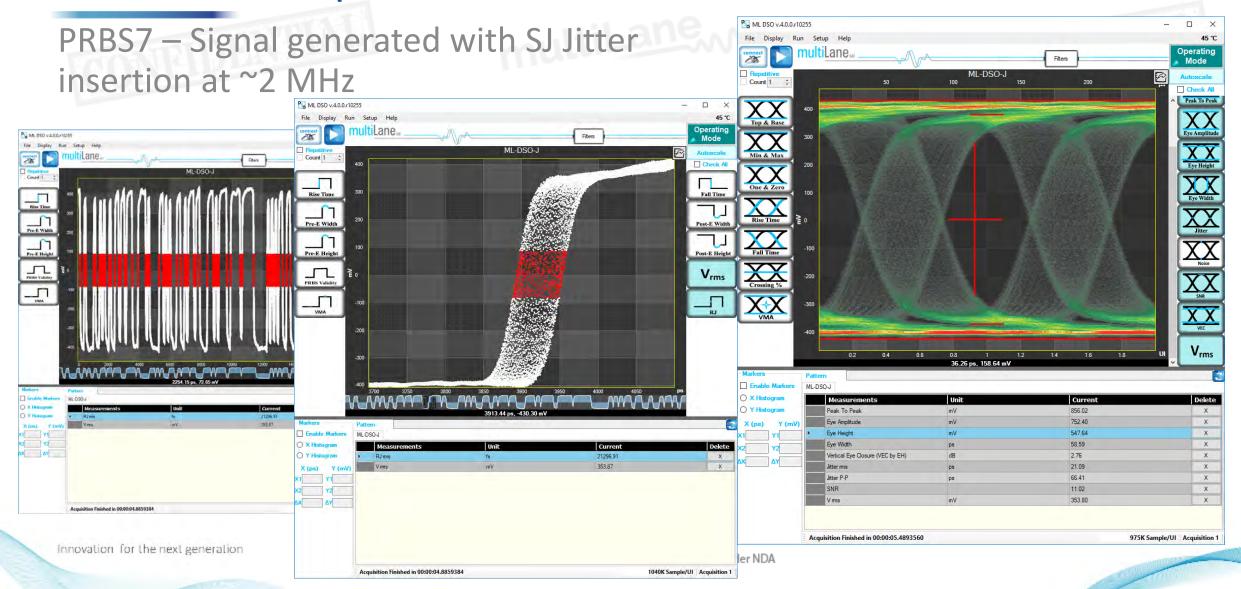

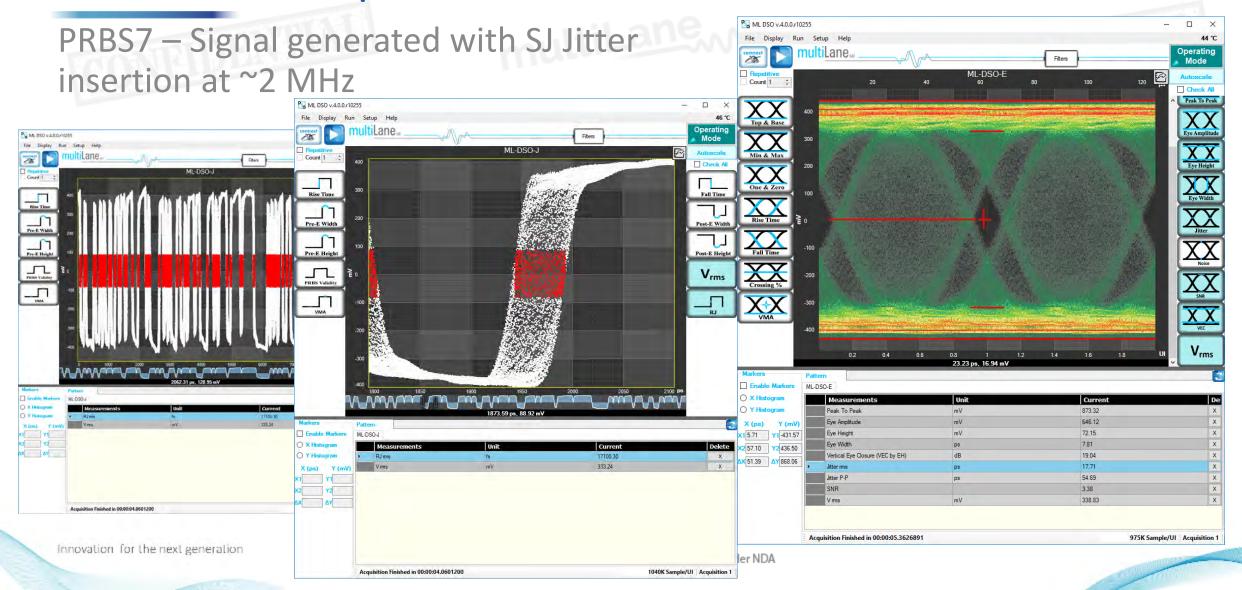

PRBS11 – Signal generated with SJ Jitter insertion at ~2 MHz

Jitter injected by software

PRBS11 – Signal generated with SJ Jitter insertion at ~10 MHz

Jitter injected by software

PRBS11 – Signal generated with SJ Jitter insertion at ~100 MHz

Jitter injected by software

PRBS11 – Signal generated with SJ Jitter insertion at ~100 MHz (60 ps) with Amplitude Control

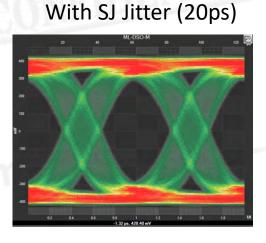

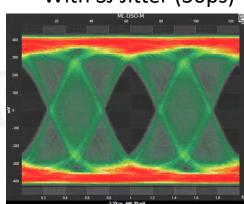

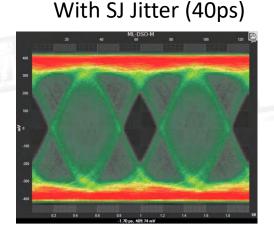

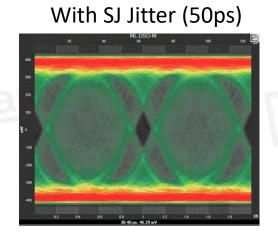

Jitter injected by software (50 ps)

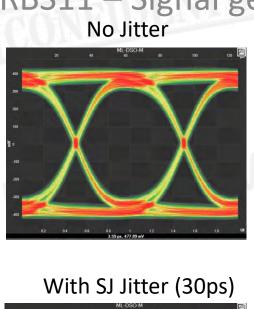

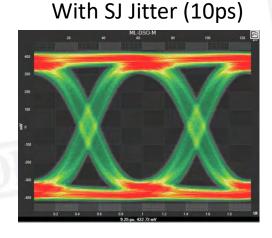

PRBS11 – Signal generated with SJ Jitter insertion at ~2 MHz

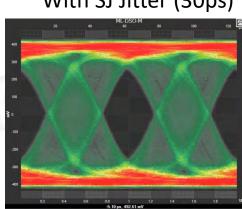

With SJ Jitter (5ps)

ML050-M

Innovation for the next generation

Confidential and Proprietary: Shared under NDA

PRBS11 - Signal generated with SJ Jitter insertion at ~10 MHz

Innovation for the next generation

PRBS11 – Signal generated with SJ Jitter insertion at ~100 MHz

With SJ Jitter (5ps)

Innovation for the next generation

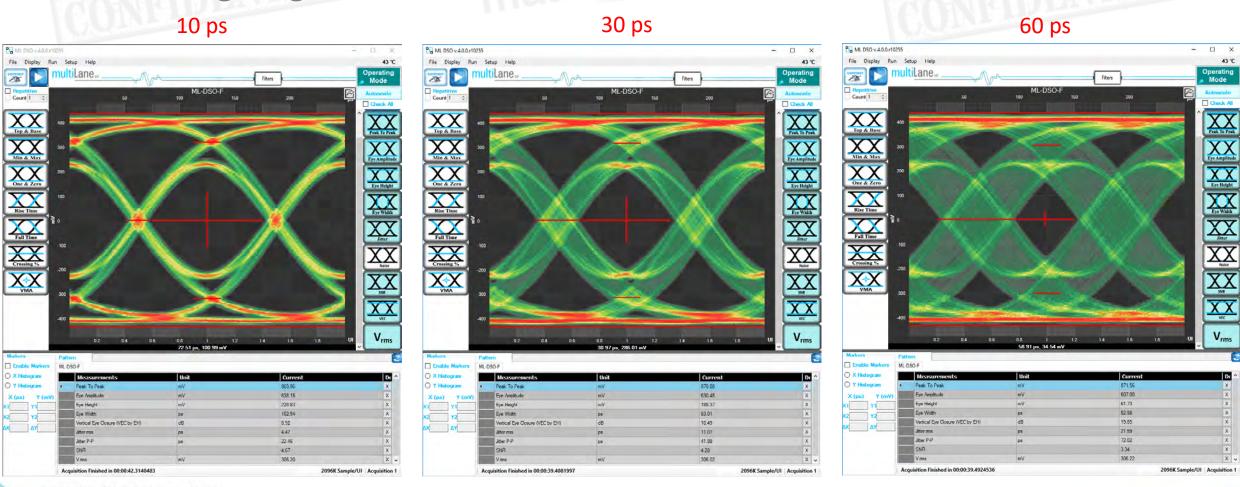

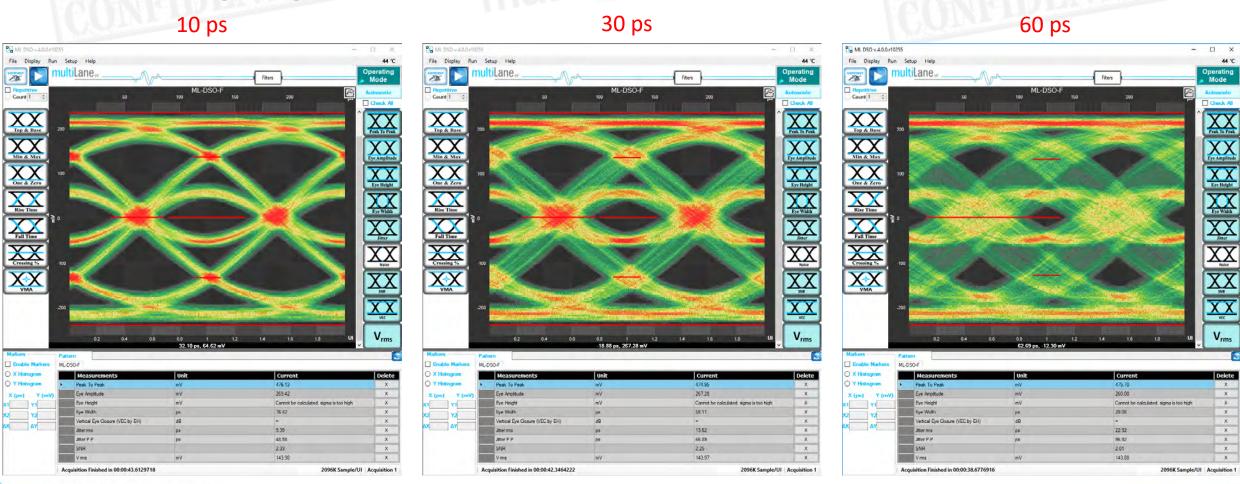

#### Jitter Measurements – PRBS 11

ISI emulation and single tone Jitter injection by software for PCIe Gen 3

# PCle Gen3 8Gbps – SJ Jitter and ISI injection at Tx

PRBS11 – Signal generated with SJ Jitter insertion at ~2 MHz and ISI at 6dB

# PCle Gen3 8Gbps – SJ Jitter and ISI injection at Tx

PRBS11 – Signal generated with SJ Jitter insertion at ~10 MHz and ISI at 6dB

# PCle Gen3 8Gbps – SJ Jitter and ISI injection at Tx

PRBS11 – Signal generated with SJ Jitter insertion at ~100 MHz and ISI at 6dB

PRBS11 – Signal generated with SJ Jitter insertion at ~2 MHz and ISI at 12dB

PRBS11 – Signal generated with SJ Jitter insertion at ~10 MHz and ISI at 12dB

PRBS11 – Signal generated with SJ Jitter insertion at ~100 MHz and ISI at 12dB

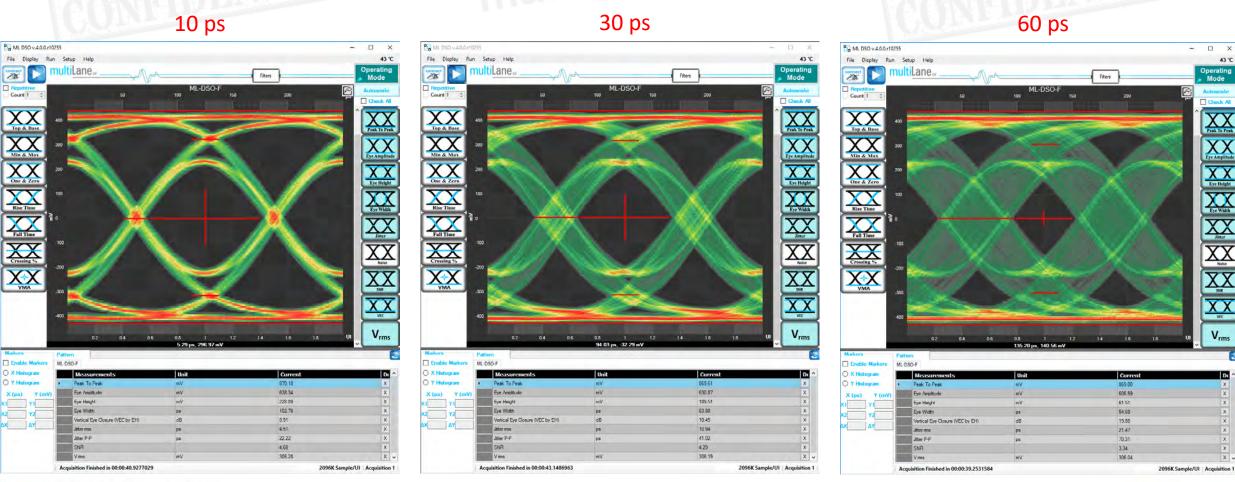

## Jitter Measurements – PRBS 11

Dual tones Jitter injection by software for PCle Gen 4

PRBS11 – SJ Amplitude 2 ps at ~60 MHz and ~1 MHz with ISI at 6dB

PRBS11 – SJ Amplitude 2 ps at ~60 MHz and ~4 MHz with ISI at 6dB

PRBS11 – SJ Amplitude 5 ps at ~60 MHz and ~1 MHz with ISI at 6dB

PRBS11 – SJ Amplitude 5 ps at ~60 MHz and ~4 MHz with ISI at 6dB

PRBS11 – SJ Amplitude 10 ps at ~60 MHz and ~1 MHz with ISI at 6dB

PRBS11 – SJ Amplitude 10 ps at ~60 MHz and ~4 MHz with ISI at 6dB

PRBS11 – SJ Amplitude 20 ps at ~60 MHz and ~1 MHz with ISI at 6dB

PRBS11 – SJ Amplitude 20 ps at ~60 MHz and ~4 MHz with ISI at 6dB

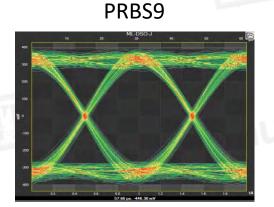

# PCle Gen3 8Gbps – PRBS 9

BUJ injection based on PN5 aggressor signal addition to emulate cross-talk

# PCle Gen3 8Gbps – PRBS 9

BUJ injection based on PN5 aggressor (0.1 SNR) signal addition to emulate cross-talk

# PCle Gen3 8Gbps – PRBS 9

BUJ injection based on PN5 aggressor (0.2 SNR) signal addition to emulate cross-talk

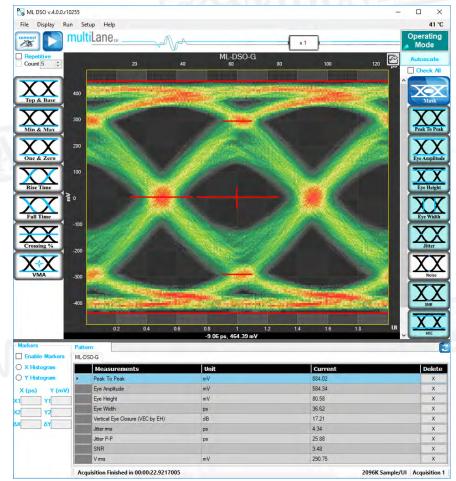

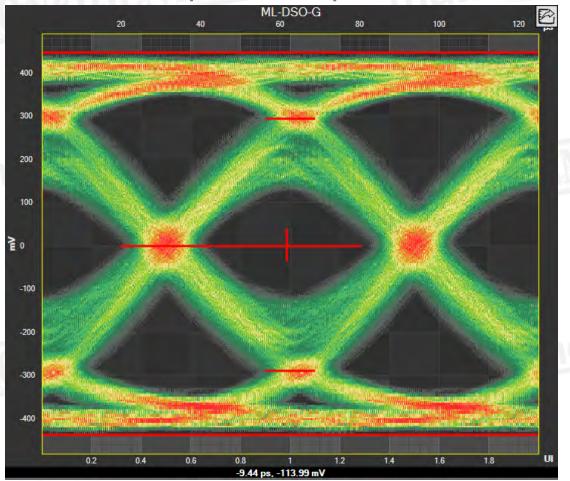

# PCle Gen4 16Gbps – PRBS 9

BUJ injection based on PN5 aggressor (0.1 SNR) signal addition to emulate cross-talk

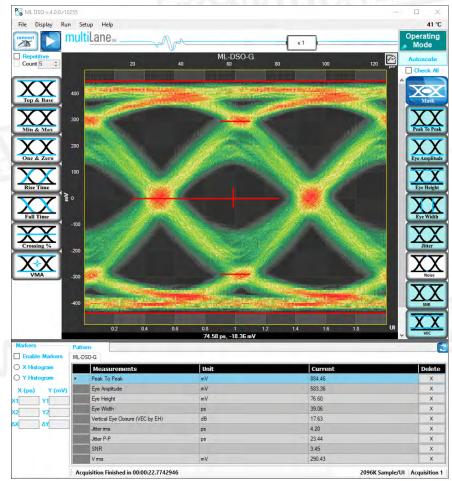

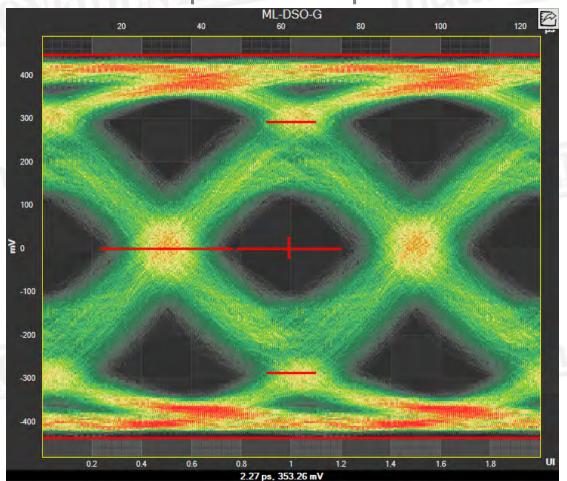

# PCle Gen4 16Gbps – PRBS 9

BUJ injection based on PN5 aggressor (0.2 SNR) signal addition to emulate cross-talk

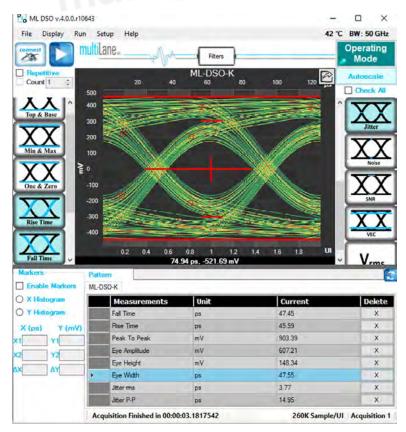

# PCle Gen4 16Gbps – PRBS 7

De-embedding s-parameters by applying customized patterns after pre-processing

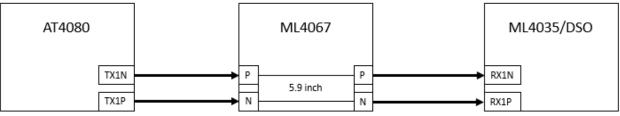

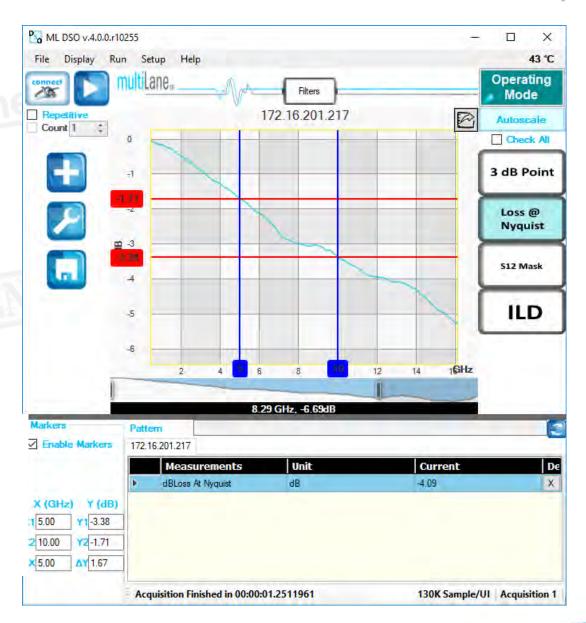

## 4080 Product

Insertion Loss addition using ML4067 (5.9 inches) and De-embedding

## 4080 Product

## Insertion Loss addition using ML4067 (5.9 inches) and De-embedding

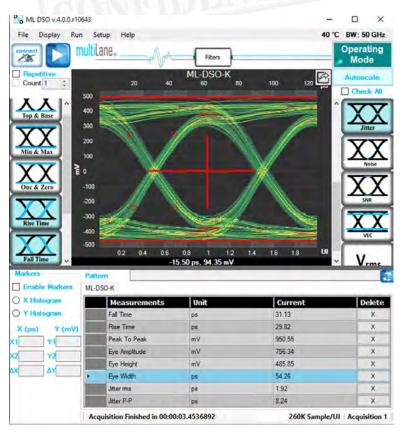

PRBS7 16 Gbps – Reference signal

PRBS7 16 Gbps with 5.9 inches

PRBS7 16 Gbps after De-embedding

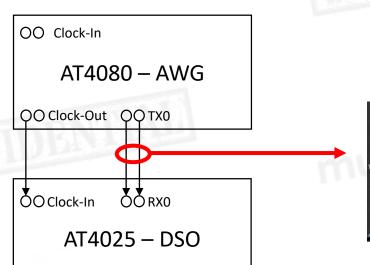

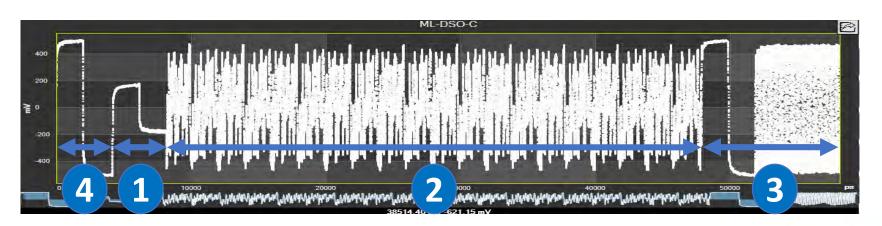

### PCle 6.0 Jitter Measurement Pattern – Requirements

### Pattern generation using AT4080

- Jitter Measurement Pattern is a 52 UI repeating sequence consisting of 4 sets of 13 UI per set

- Covers all 12 level transitions

- 12 transitions \* 4 sets = 48 edge transitions

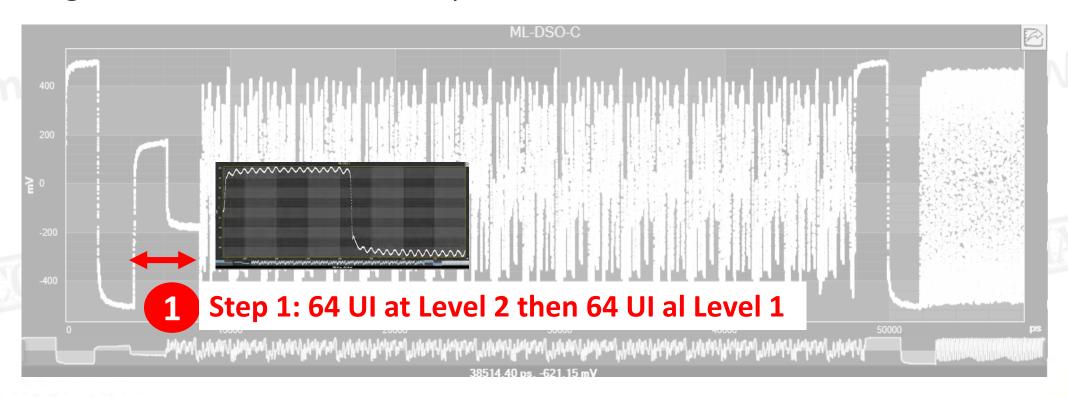

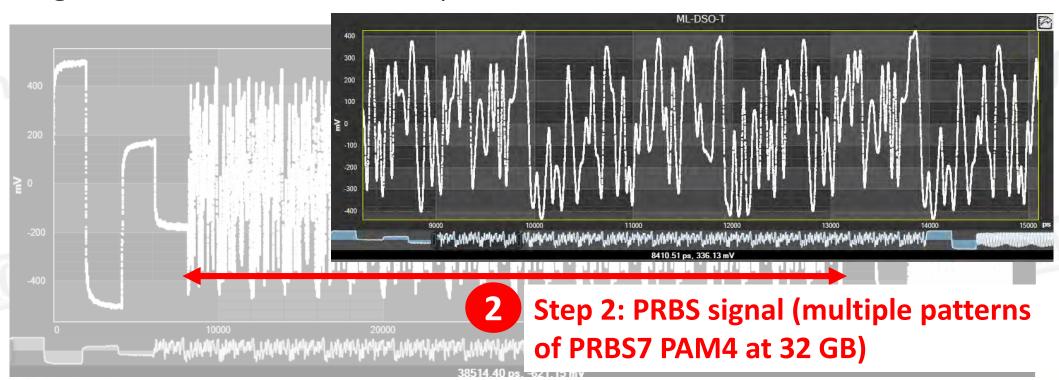

PCIe 6.0 Compliance Pattern Generation – Requirements

- Step 1: 64 UI at Level 2 then 64 UI al Level 1

- Step 2: PRBS signal

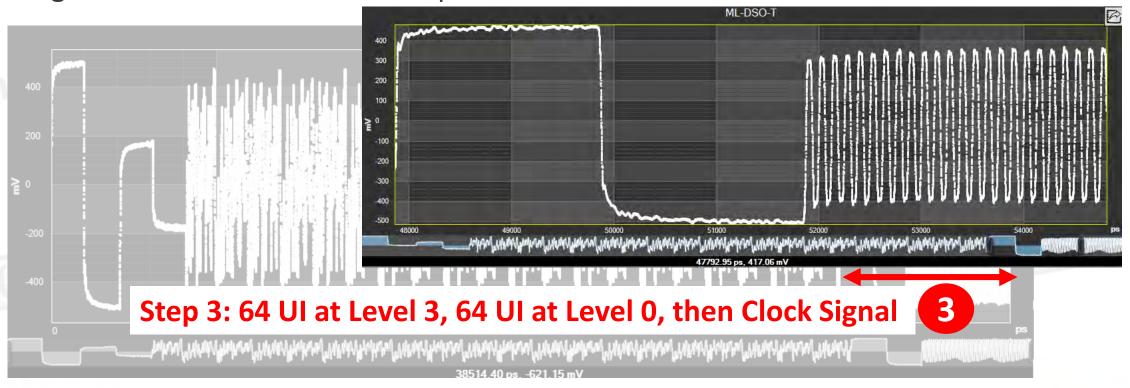

- Step 3: 64 UI at Level 3, 64 UI at Level 0, then Clock Signal

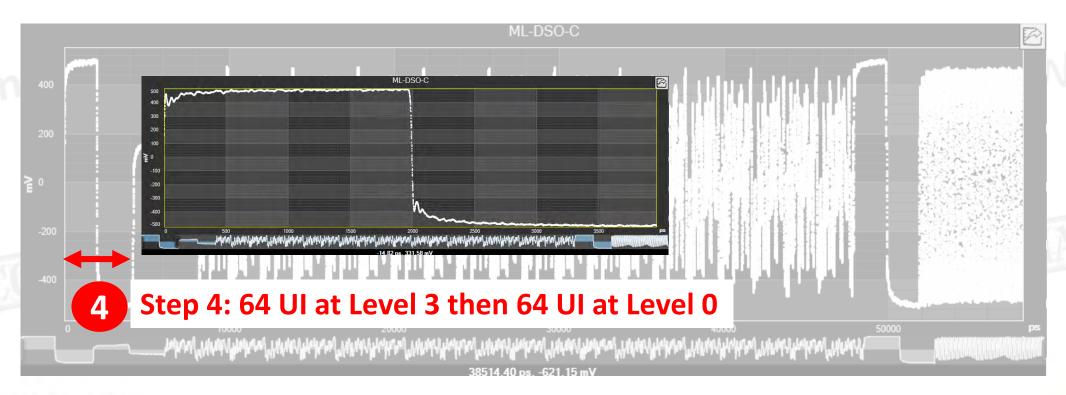

- Step 4: 64 UI at Level 3 then 64 UI at Level 0

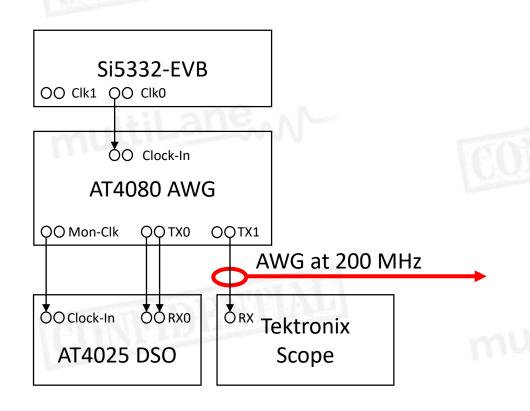

PCIe 6.0 Compliance Pattern – Test results using ML products

PCIe 6.0 Compliance Pattern – Test results using ML products

PCIe 6.0 Compliance Pattern – Test results using ML products

PCIe 6.0 Compliance Pattern – Test results using ML products

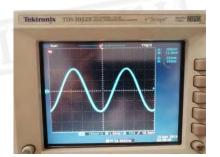

Generation of external reference clock from Si5332-EVB with SSC capability

Generation of external reference clock from Si5332-EVB with SSC capability

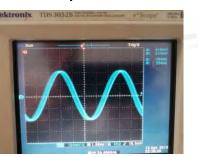

### SSC disabled

### SSC enabled

Down Spread 2.5%

Generation of external reference clock from Si5332-EVB with SSC capability

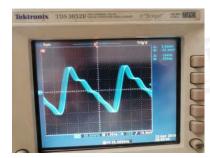

### SSC disabled

Down Spread 2.5%

### SSC enabled

Generation of external reference clock from Si5332-EVB with SSC capability

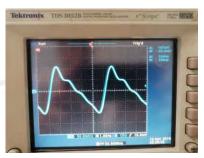

**SSC** disabled

Down Spread

- Hillane

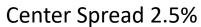

Down Spread 2.5% Center Spread 2.5%

SSC enabled

Generation of external reference clock from Si5332-EVB with SSC capability

### **SSC** disabled

### SSC enabled

Generation of external reference clock from Si5332-EVB with SSC capability

### **SSC** disabled

### SSC enabled

Generation of external reference clock from Si5332-EVB with SSC capability

### **SSC** disabled

### SSC enabled

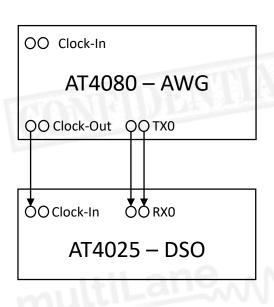

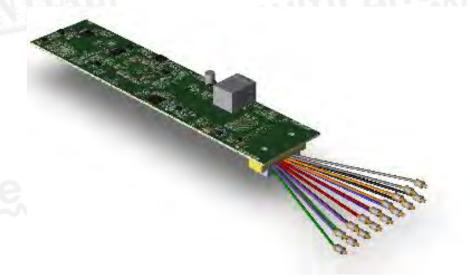

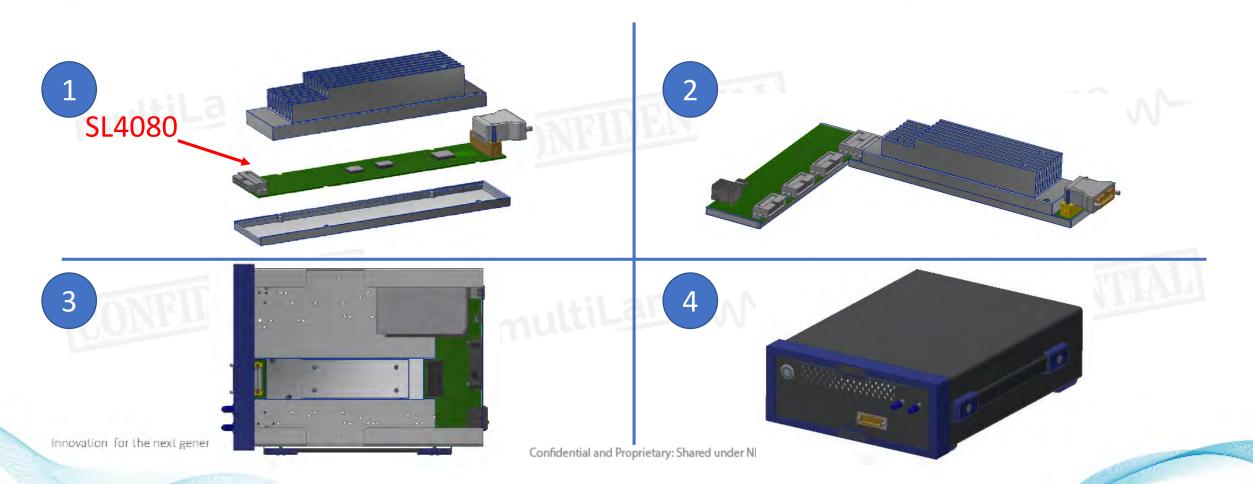

## 4080 Mechanical Overview

## Available as AT4080, SL4080 and ML4080

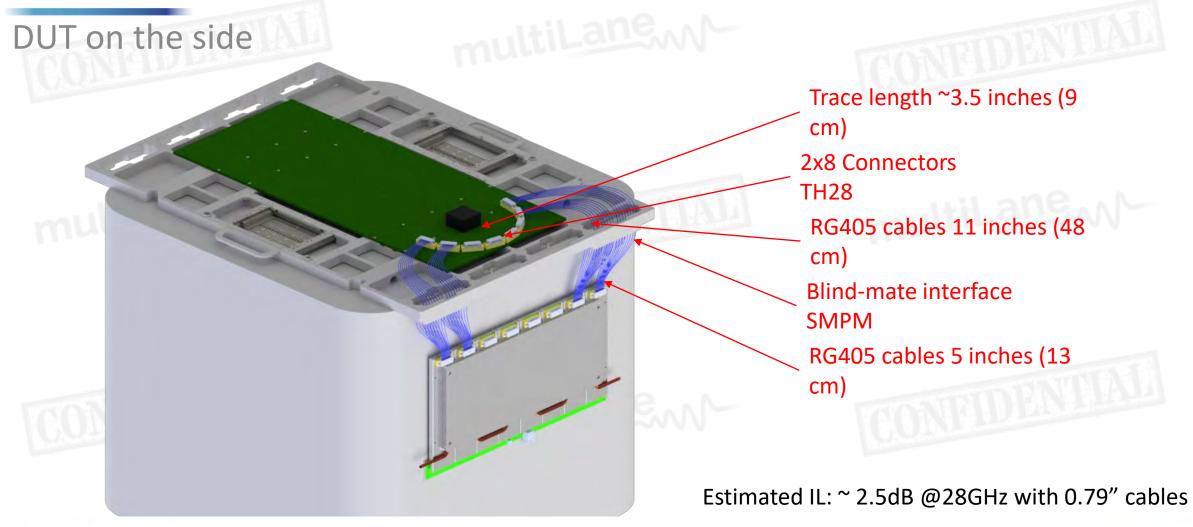

AT4080: customized to fit and function inside an Advantest HSIO test head extender. One cassette can host up to 2xAT4080  SL4080: customized to fit on a backplane on the side of the test head.

## 4080 Mechanical Overview

## Available as AT4080, SL4080 and ML4080

ML4080: integrating the SL4080 into black box

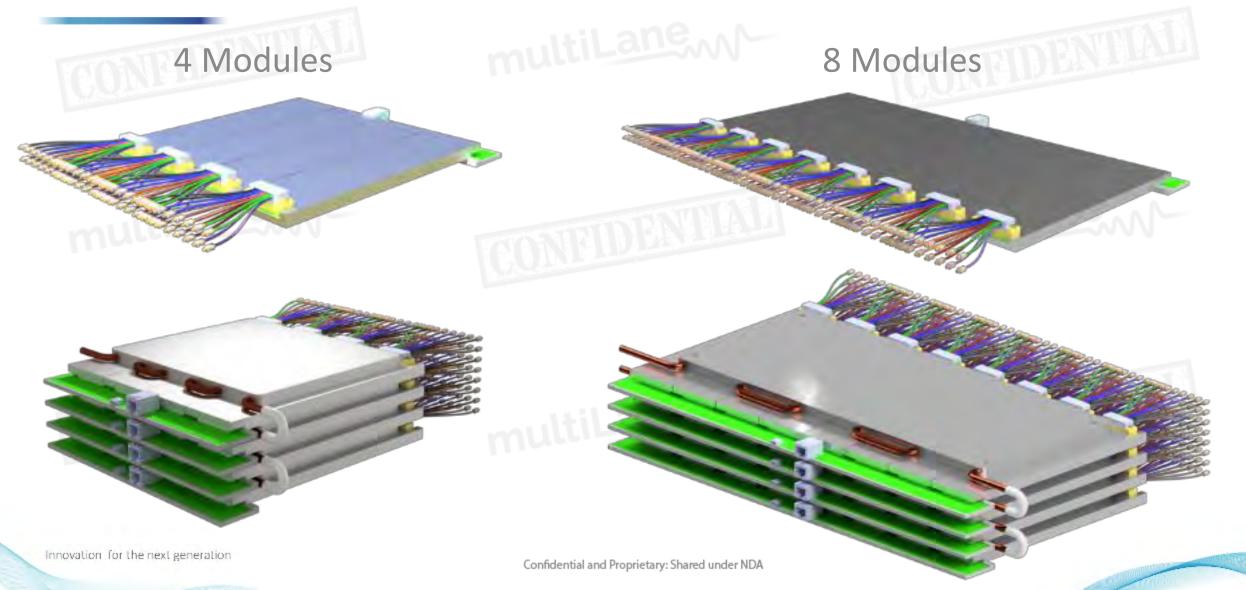

## **Slices Overview**

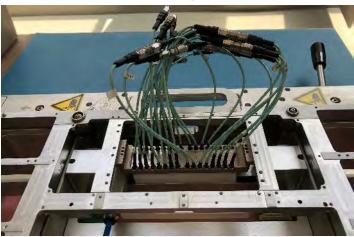

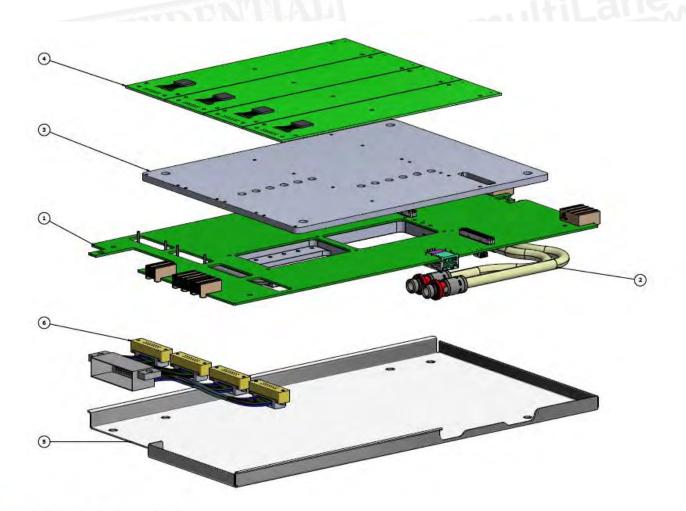

# SL4080 Slices on Carrier | Exploded View

| PARTS LIST |     |                              |                        |

|------------|-----|------------------------------|------------------------|

| ITEM       | QTY | PART NUMBER                  | DESCRIPTION            |

| 1          | 1   | Carrier-PCB                  |                        |

| 2          | 1   | HEAT SINK Customized         | Customized Cooling Bar |

| 3          | 1   | heat transfer plate Option 2 |                        |

| 4          | 4   | DC                           | Slice Cards            |

| 5          | 1   | Cover                        |                        |

| 6          | 4   | TH28-RA To J10               | 2x8 Coax Cables to J10 |

# Integration on the Side of a Test Head

Innovation for the next generation

### North America

48521 Warm Springs Boulevard Suite 310 Fremont, CA 94539, USA +1 510 573 6388

### Worldwide

Houmal Technology Park Askarieh Main Road Houmal, Lebanon +961 81 794 455

### Asia

7th Floor-2, No. 156 Sec. 2, Dongda Road, North District, Hsinchu City 300, Taiwan (R.O.C.) +886 3 5744 591

### UAE

Building 4WA, Office 420 Dubai Airport Freezone Authority, Dubai UAE +971 4 548 7 547